## LOW LEVEL RADIO FREQUENCY CONTROL OF RIA SUPERCONDUCTING CAVITIES

By

Michael John O'Farrell

### A THESIS

Submitted to Michigan State University in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

Department of Electrical and Computer Engineering

2005

UMI Number: 1428960

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

#### UMI Microform 1428960

Copyright 2006 by ProQuest Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

### ABSTRACT

## LOW LEVEL RADIO FREQUENCY CONTROL OF RIA SUPERCONDUCTING CAVITIES

By

Michael John O'Farrell

High velocity superconducting radio frequency (SRF) cavity designs at MSU, for the proposed Rare Isotope Accelerator (RIA), have an unloaded Q on the order 10e9. RIA applications use low beam currents resulting in loaded Qs of the order 10e7. In order to maintain stable fields, RF power requirements will be dominated by control of the cavity fields in the presence of low-level perturbations on the cavity.

A field programmable gate array (FPGA) based, low level radio frequency (LLRF) controller has been designed to compensate for perturbations on accelerating cavities, maintaining driving amplitude and phase levels, on a point-by-point basis, thereby stabilizing cavity fields. Originally designed at Lawrence Berkeley National Labs, for use at another accelerator project, the controller was adapted for use on RIA prototype medium beta cavities. Supporting circuitry was designed and built for cavity controls, and its performance was measured.

The emphasis of this thesis concerns the understanding of the digital control loop, its implementation at the National Superconducting Cyclotron Laboratory for RIA, and an analysis of the controller's performance.

This thesis is for my beautiful bride Ivana, Ethan and Madeline for whom I returned to school.

## ACKNOWLEDGMENTS

I would like to thank everyone in the electronic department at the NSCL, for making me feel at home and providing me with not only technical aid but a stimulating environment. I would especially like to thank John Vincent for his help in directing the work for microphonics, and supporting me both with funding and the direction and learning required to understand the workings at the lab. I also would like to thank Terry Grimm for his help and leadership. There are a couple of friends in the lab that I could not have achieved the results of the this thesis, John Popielarski, Adam Molzahn, and Tarek Kandil.

I must acknowledge Leo Kempel for his help and instruction over the last three years, making my time at MSU more interesting. I thank Dr. Kempel for getting me in at one of the coolest workplaces a graduate student could wish for.

Finally, my children Ethan and Madeline and my wife Ivana, who has provided me with unending love and support right from the start.

Thank you

# TABLE OF CONTENTS

| A | BSTR   | ACT                                          | ii  |

|---|--------|----------------------------------------------|-----|

| A | CKNO   | WLEDGMENTS                                   | iv  |

| L | IST OF | TABLES                                       | iii |

| L | IST OF | FIGURES                                      | ix  |

| 1 | Introd | luction                                      | 1   |

| 2 | Cavit  | y Parameters                                 | 7   |

|   | 2.1    | Description of the SRF                       | 7   |

|   | 2.2    | Circuit Model of the Cavity                  | 8   |

|   | 2.3    | Resonator Description and Simplification     | 12  |

|   | 2.4    | Beam Dynamics                                | 13  |

|   | 2.5    | Derivation of the Quality Factor             | 15  |

|   |        | 2.5.1 Additional Quality Factors of Interest | 17  |

|   | 2.6    | Tuning Angle and Cavity Voltage Requirements | 18  |

|   | 2.7    |                                              | 22  |

|   |        |                                              | 22  |

|   | 2.8    |                                              | 24  |

|   | 2.9    |                                              | 25  |

| 3 | Mitig  | ation of Disturbances                        | 26  |

|   | 3.1    |                                              | 26  |

|   | 3.2    |                                              | 27  |

|   | • · -  |                                              | 27  |

|   |        |                                              | 28  |

|   |        | 0                                            | 28  |

|   |        |                                              | 30  |

|   | 3.3    |                                              | 32  |

|   | 3.4    | C                                            | 34  |

|   | 3.5    | 6                                            | 34  |

| 4 | Signa  | l Capture                                    | 35  |

|   | 4.1    |                                              | 35  |

|   | 4.2    |                                              | 35  |

|   | 4.3    |                                              | 36  |

|   | 4.4    |                                              | 39  |

|   | 4.5    | - 8 - 1 - 8                                  | 43  |

|   |        |                                              | 43  |

|   |        | Ç                                            | 44  |

|   |        |                                              | · · |

|   | 4.6  | An I/Q Sample Example                      | 5 |

|---|------|--------------------------------------------|---|

|   | 4.7  | Conclusion                                 | 0 |

|   |      |                                            |   |

| 5 | •    | al Flow                                    |   |

|   | 5.1  | Introduction                               |   |

|   | 5.2  | Proportional Integrator Controllers        |   |

|   | 5.3  | Z-transform                                |   |

|   | 5.4  | LLRF Operational Data Input and Set Points | 6 |

|   |      | 5.4.1 Direct Digital Synthesis             | 7 |

|   |      | 5.4.2 CORDIC                               | 8 |

|   |      | 5.4.3 Error signal                         | 0 |

|   | 5.5  | Follow the Bit Path                        | 1 |

|   |      | 5.5.1 Inputs                               | 4 |

|   |      | 5.5.2 Proportional Gain                    | 5 |

|   |      | 5.5.3 Integrator                           | 6 |

|   |      | 5.5.4 Compensated Output                   | 7 |

|   | 5.6  | Digital-Analog Converter Output            | 8 |

|   | 5.7  | Conclusion                                 |   |

|   | 211  |                                            | - |

| 6 | Anal | g Signal Preparation                       | 2 |

|   | 6.1  | Introduction                               | 2 |

|   | 6.2  | Signal Level Requirements                  | 3 |

|   | 6.3  | Reference Signal                           | 5 |

|   | 6.4  | LLRF Support Chassis                       | 7 |

|   |      | 6.4.1 Overall Implementation               | 8 |

|   |      | 6.4.2 RF Design Techniques                 | 9 |

|   | 6.5  | Schematic                                  |   |

|   | 6.6  | Conclusion                                 |   |

|   | 0.0  |                                            | Ť |

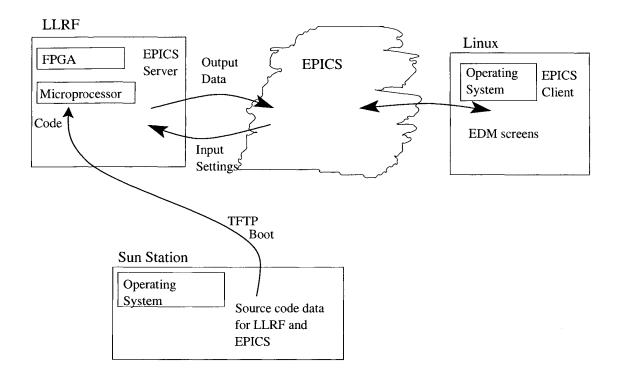

| 7 | Link | from PC to LLRF                            | 4 |

|   | 7.1  | Introduction                               | 4 |

|   | 7.2  | SUN Station                                | 4 |

|   | 7.3  |                                            | 5 |

|   | 7.4  | Linux                                      | 6 |

|   | 7.5  |                                            | 6 |

|   | 7.6  | 0                                          | 7 |

|   |      |                                            |   |

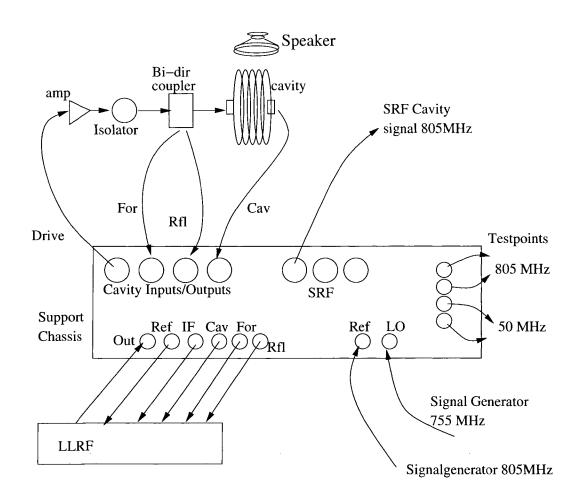

| 8 | Data | verification                               | 8 |

|   | 8.1  | Introduction                               | 8 |

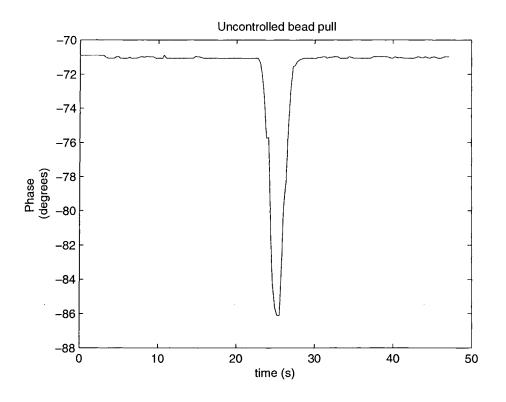

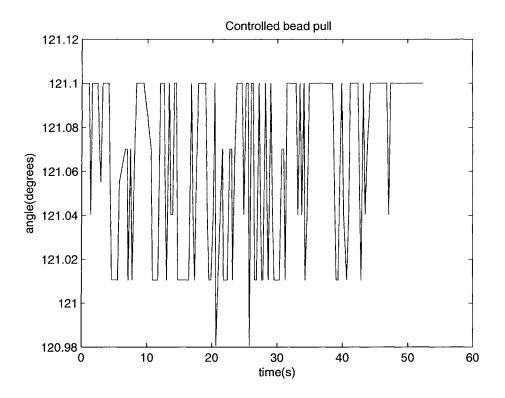

|   | 8.2  | Bead Pull                                  | 0 |

|   | 8.3  | Performance of Phase Compensation          | 2 |

|   |      | 8.3.1 Noise Floor                          |   |

|   | 8.4  | Amplitude performance                      |   |

|   | 8.5  | Conclusions                                |   |

|   | ~    |                                            | · |

| 9 Conclusion and Future Work      |

|-----------------------------------|

| 9.1 Future Work                   |

| A User Manual                     |

| A.1 Hardware and Software         |

| A.2 Connection and set-up         |

| A.2.1 Connection on rear          |

| A.2.2 Front panel                 |

| A.3 Explain all parameters on GUI |

| A.3.1 Main                        |

| A.3.2 Extra                       |

| A.3.3 Config Reg                  |

| A.3.4 Phase plots                 |

| A.4 Start and calibration         |

| A.5 Additional Controls           |

| A.6 Viewgraphs                    |

| A.7 Manipulating EDL              |

| B LLRF Schematic                  |

| BIBLIOGRAPHY                      |

## LIST OF TABLES

| 1.1 | Numbers and types of cavities in RIA linac    |

|-----|-----------------------------------------------|

| 5.1 | I/Q values from set-I                         |

| 5.2 | Example of CORDIC rotation of set-points      |

| 6.1 | LLRF Input signal labels and levels           |

| 6.2 | Anticipated output levels from cavity         |

| 8.1 | List of components used in test               |

| 8.2 | Measured noise of the attenuator              |

| 8.3 | All phase errors, measured vs calculated      |

| 8.4 | Percent deviation of amplitude from set-point |

| 8.5 | Percent deviation of measured values to EPICS |

| 8.6 | Percent deviation of amplitude from set-point |

| A.1 | ADC signal level response to IF input levels  |

| A.2 | ADC signal level response to LO input levels  |

| A.3 | Mode register setting                         |

| A.4 | Mode settings                                 |

# LIST OF FIGURES

| 1.1<br>1.2                                                                                                                      | Illustration of various linac cavities                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3<br>3                                           |

|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> <li>2.9</li> </ol> | General system set-up for a single 6-cell elliptical cavity                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9<br>9<br>11<br>12<br>13<br>14<br>17<br>19<br>25 |

| 3.1<br>3.2<br>3.3                                                                                                               | Self Excited Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29<br>30<br>33                                   |

| 4.1<br>4.2<br>4.3                                                                                                               | Signal $f_a$ sampled at $f_s$                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40<br>41                                         |

| 4.4<br>4.5<br>4.6<br>4.7                                                                                                        | tical sampled data spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42<br>43<br>47<br>48<br>49                       |

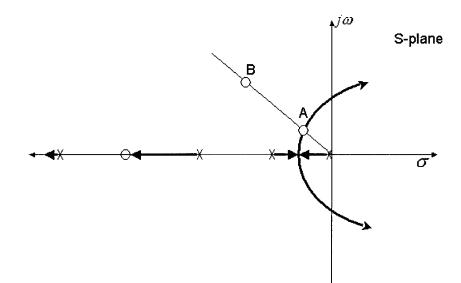

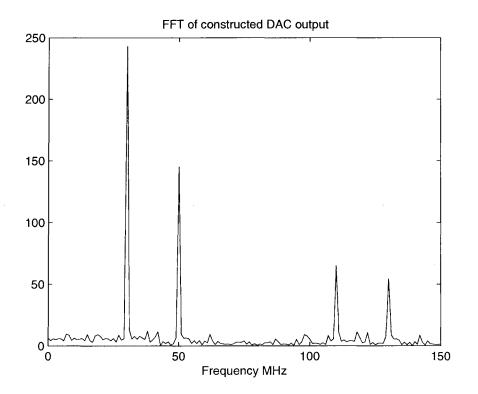

| 5.11<br>5.12                                                                                                                    | Closed loop system.<br>Example root locus where A is stable and B is higher gain but not stable.<br>Block diagram of a PI compensator.<br>Example z-plane plot of $H(z)$ .<br>Simulated plot of CORDIC output.<br>Flow chart of digital data and processing for PI.<br>Set-point creation by DDS and Cordic.<br>Proportional gain.<br>Integrater.<br>Final adder and output.<br>DAC output with additional points from 'afterburner'.<br>Frequency spectrum of DAC output with additional points. | 64<br>65<br>67<br>67<br>69<br>70                 |

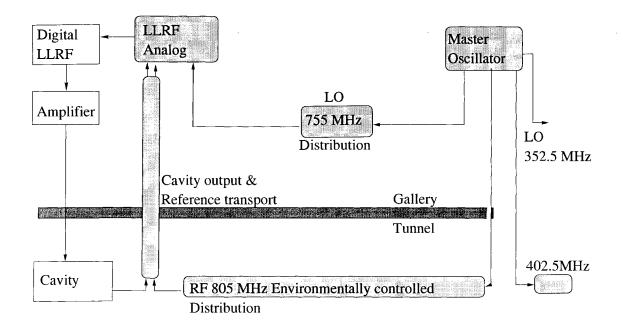

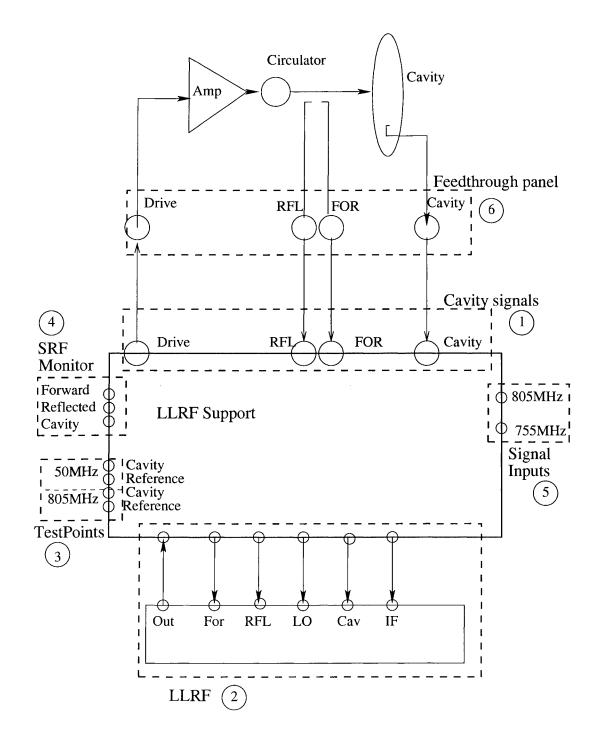

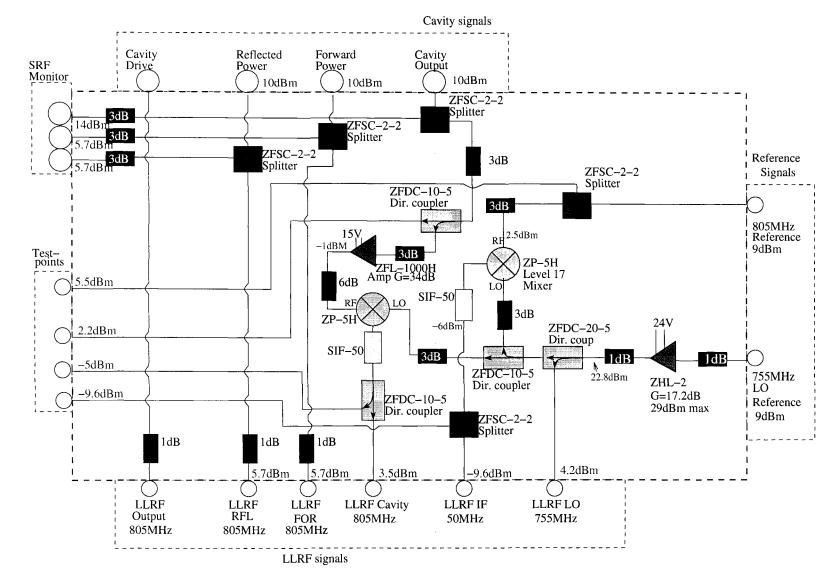

| 6.1<br>6.2<br>6.3                                                                                                               | Example of reference distribution from SNS                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 75<br>76<br>82                                   |

| 6.4  | LLRF Support chassis schematic                                                                 |

|------|------------------------------------------------------------------------------------------------|

| 7.1  | Relationship between hardware components                                                       |

| 7.2  | Example EDL screenshot                                                                         |

| 8.1  | Test set-up for support chassis                                                                |

| 8.2  | $15.1^{\circ}$ phase disturbance from an uncontrolled bead pull 91                             |

| 8.3  | $0.12^{\circ}$ phase disturbance from a controlled bead pull. $\ldots \ldots \ldots \ldots 92$ |

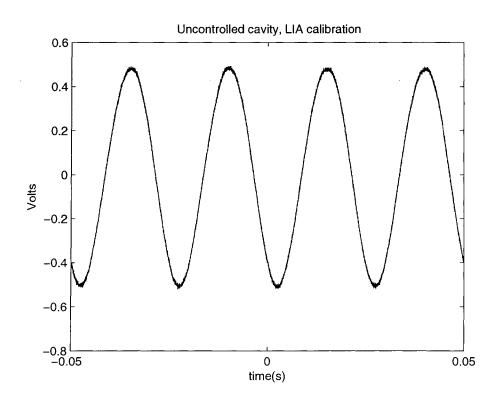

| 8.4  | Cavity phase measurement with Lock-in-Amplifier at $18^{\circ}$                                |

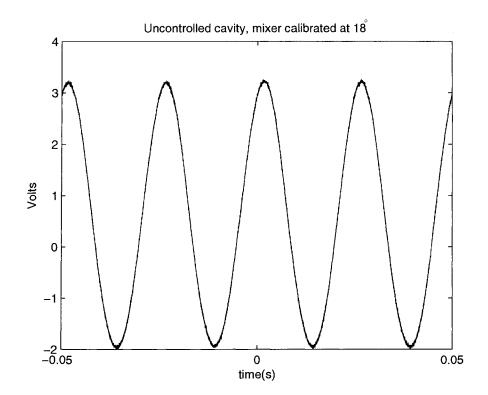

| 8.5  | '805 mixer error' measurement at 18.216°                                                       |

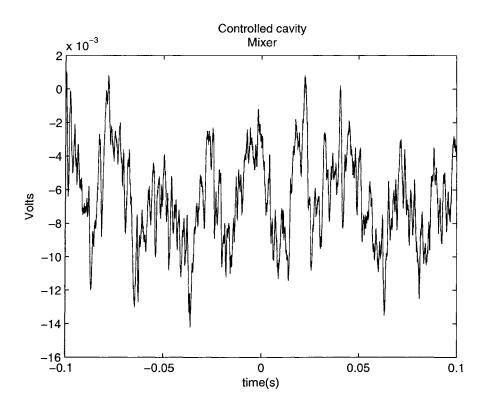

| 8.6  | Controlled cavity mixer error measurement of 0.0526°                                           |

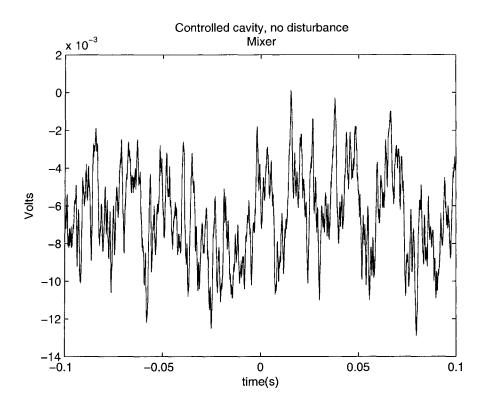

| 8.7  | Controlled cavity with no disturbance resulting in $0.045^{\circ}$ error 98                    |

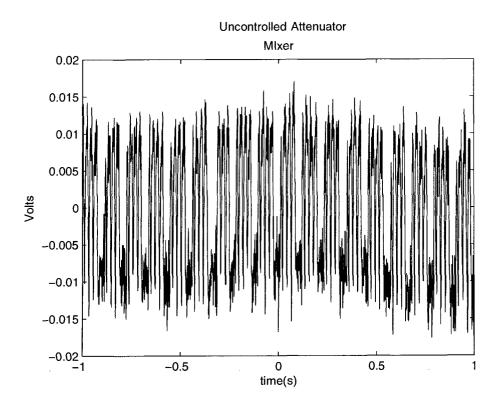

| 8.8  | Phase error of uncontrolled attenuator equates 0.1198°                                         |

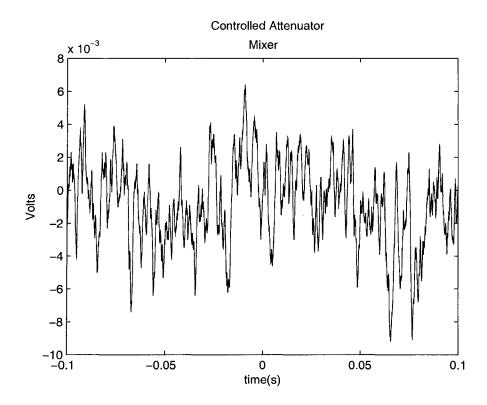

| 8.9  | Phase error of controlled Attenuator equates to 0.054°                                         |

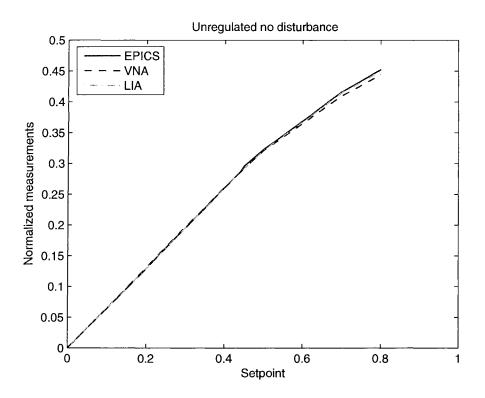

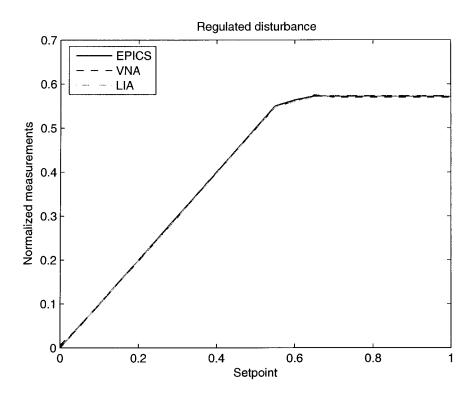

| 8.10 | Amplitude measurements vs. set-point, uncontrolled and no disturbance 102                      |

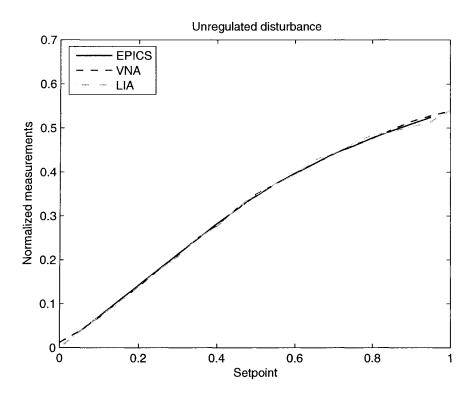

| 8.11 | Amplitude measurements vs. set-point, uncontrolled with a disturbance 103                      |

| 8.12 | Amplitude measurements vs. set-point, controlled with a disturbance 104                        |

| B.1  | LLRF schematic                                                                                 |

# **CHAPTER 1**

# Introduction

Increased pressure from the physics community for further research into nuclear particle physics has created a demand for high velocity, high energy accelerators. Superconducting cavities are capable of supporting high fields with low power losses due to the reduced surface resistances. The quality factor (Q) of a cavity is indicative of how high the fields can be achieved. Higher Q-factors represent stronger internal fields, but with a more narrow bandwidth. In the presence of perturbations, maintaining amplitude and phase control, or field stability becomes increasingly difficult with very high Q-factors, because of the associated narrow bandwidths. Superconducting Radio Frequency (SRF) cavity prototypes, designed and built at Michigan State University (MSU) for the proposed Rare Isotope Accelerator (RIA), have obtained an unloaded Q of 10<sup>10</sup>. Loaded Q-factors of magnitude 10<sup>7</sup> are anticipated during beam operation. Maintaining amplitude and phase of such high Q cavities is only possible with digital controllers capable of compensating for disturbances as they occur.

A low level radio frequency (LLRF) controller, designed for Spallation Neutron Source (SNS), and built at Lawrence Berkeley National Labs (LBNL) in collaboration with Los Alamos Labs, was acquired by the National Superconducting Cyclotron Laboratory (NSCL) for phase and amplitude control of SRF cavities. This thesis is based on the implementation and operation of the controller. In order to understand the operation of the controller, a background review of electromagnetics, particle physics, control systems, signal processing, digital signal processing and VHDL is presented. Verification of the output data is performed and finally a user manual is attached as an appendix.

| Туре                       | Six-cell elliptical |      |      | Triple spoke |      |

|----------------------------|---------------------|------|------|--------------|------|

| $\beta_{opt}$              | 0.49                | 0.63 | 0.83 | 0.50         | 0.62 |

| Number of cavities         | 68                  | 64   | 32   | 42           | 96   |

| Total                      | 164                 |      |      | 138          |      |

| Temperature( $K^{\circ}$ ) | 2                   |      |      | 4.2          |      |

Table 1.1. Numbers and types of cavities in RIA linac.

In 2004, the Department of Energy deemed (RIA) as a high priority for further research in physics. Beam physicists search for new isotopes of known elements by colliding high energy beams of specific ions onto targets of known materials, creating isotopes which are used for the advancement of materials and medicine. RIA would extend research to isotopes of heavier elements [1].

The NSCL SRF research group designed a proposal for RIA which specified the ability to accelerate ions up to uranium to 400MeV/u to high energy, with a final beam power of 400kW [3]. The number of cavities in the linear accelerator (linac) are listed in table 1.1.

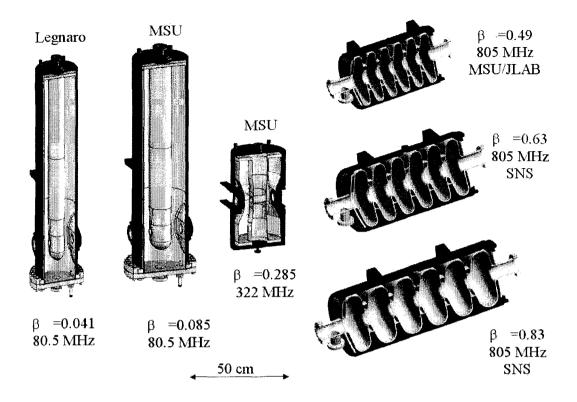

To achieve required beam powers, the linac is designed with various group of cavities. Each group is designed to allow for an increase in velocity of the beam, an example of each group is shown in figure 1.1. The  $\beta_{opt}$  is the optimum design  $\beta = \frac{v}{c}$ , where v is the velocity of the beam and c is the speed of light.

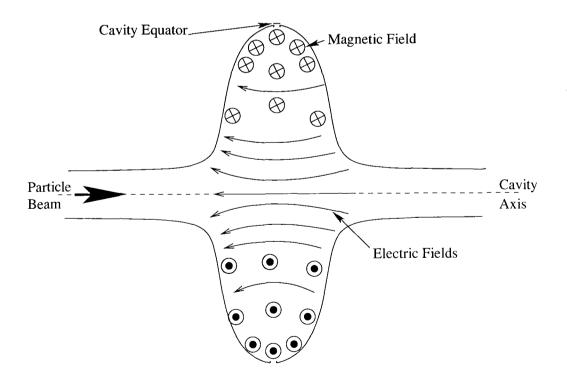

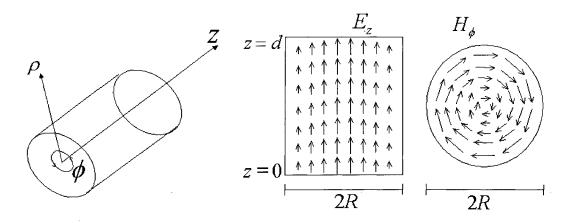

The elliptical accelerator cavity is a microwave resonator whose shape is derived from a pillbox shaped resonator. Radio frequency (RF) power is transmitted to the cavity and is coupled to the particle beam. Electric field and magnetic field patterns in the cavity are illustrated in figure 1.2, where the electric fields are normal to the metal surface, and peak electric fields occur along the center axis of the cavity. Magnetic fields patterns are azimuthal, where the peak magnetic field occur on the equator of the cavity and are zero along the center axis of the cavity [2].

The beam is accelerated through the center of the cavity axis. As the power supplied is time varying, the particles are delivered in bunches, coinciding with a harmonic of the cav-

Figure 1.1. Illustration of various linac cavities.

Figure 1.2. Cavity dynamics.

3

ity frequency. The bunches must be timed correctly to obtain the maximum acceleration. The cavity RF drive signal must be held in phase with all cavities in the linac to accelerate the beam for the length of the accelerator. If for example, the phase was offset by  $180^{\circ}$ , the beam would undergo deceleration. For beam stability all cavities are synchronized to a reference signal to accelerate the bunches of particles at the correct time.

A disturbance imposed on the cavity is observed by a change in resonant frequency. A change in resonant frequency also produces a change to the desired phase, since resonant cavities are highly dispersive, causing timing issues for the beam. Mitigating the disturbances is partially accomplished mechanically, by reducing environmental effects, and stiffening the cavity structurally to lessen sensitivity to perturbations. To compensate for disturbances, cavities have been over-coupled with power thereby lowering the  $Q_{ext}$  of the cavity. Which in turn lowers the operational  $Q_{ext}$  during beam loading. By lowering the  $Q_{ext}$ , the cavity with beam load or loaded  $Q(Q_l)$  also decreases and the effective system bandwidth increases. An increased bandwidth effectively decreases the effects of phase and amplitude offsets due to a change in resonance.

Heavier ion acceleration calls for lighter beam currents which have considerably less effect on the loaded Q of the cavity. For the low RIA beam current, it is necessary to control the resonant frequency to obtain the desired higher fields while not requiring vast amounts of power. A properly controlled system will result in significant power savings during accelerator operation [4].

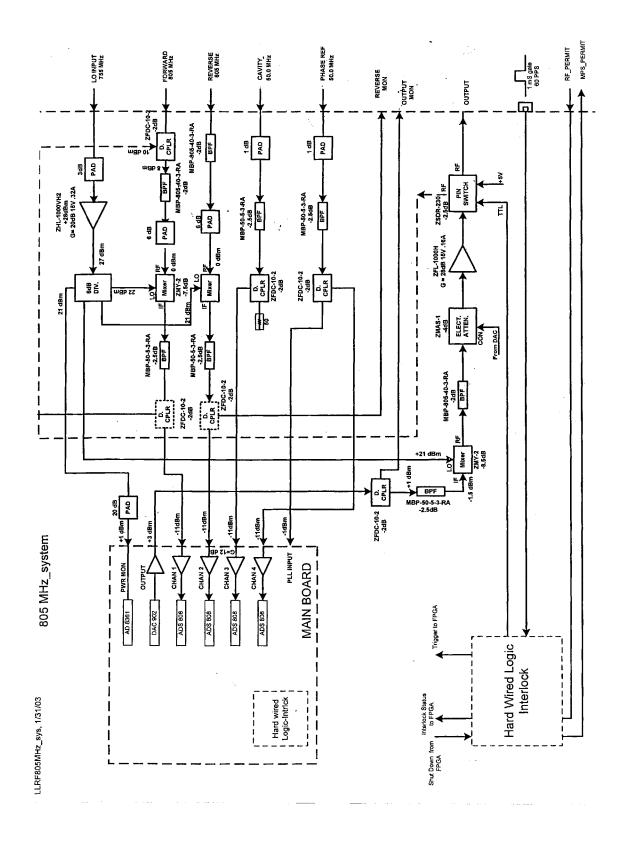

The LBNL controller is called the 'low level radio frequency' (LLRF) controller, because it is capable of compensating for microphonics as well as low level disturbances, occurring within the system bandwidth. The LLRF controller is a combination of analog signal distribution and more importantly digital design. The system is based on a Xilinx Spartan XC2S150, [12] Field Programmable Gate Array (FPGA) processor whose realtime parallel processing allows for point-by-point compensation of the RF drive signal, based on information from the cavity. To supply the controller with the appropriate signal levels, a support chassis was designed and built to support the LLRF. Testing of the cavities with the controller was completed to determine the level of performance with a five cell copper mock up cavity at room temperature.

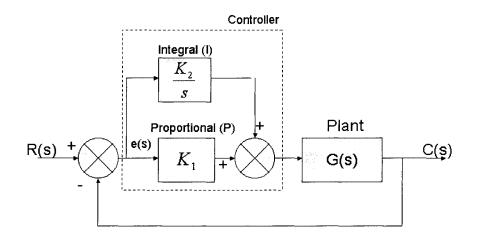

The controller is a simple Proportional Integrator control loop, but its implementation is complex. Code for the system, largely undocumented, is written in Verilog, a hardware description language, and high level C. The lack of documentation, manual, direction, and experience at NSCL has been the impetus for this thesis to evolve into a reference manual to be used for further research.

Chapter 2 is background information for the understanding of the relationship between cavity dynamics, beam physics, and the cavity de-tuning that is a result of disturbances on the cavity. A circuit model of the cavity is used to simplify some of the equations leading to the relationship of cavity input power and the limit of controllable de-tuning.

Chapter 3 describes the source of disturbances and methods previously used to mitigate these perturbations. Discussion leads to a digital method of controlling the cavity and how it may be implemented into a linac.

Background information regarding analog and digital demodulation of signals is presented in Chapter 4. A method of capturing signal information in the rectangular form of complex real and imaginary values (I and Q), is explained, in addition to analog to digital conversion (ADC). The method of signal capture for digital processing in the controller is established and discussed. Chapter 5 concerns a detailed breakdown of the digital control aspect of compensation, along with some of the additional functionality.

Chapter 6 discusses the method of distributing and supplying analog signals at the correct level to the ADC for proper signal capture. A support chassis was designed and built to house components and supply the appropriate level signals to the LLRF. The relationship between graphical user interfaces, supporting computers and the LLRF are explained in Chapter 7. The analysis of the support chassis design and the accuracy of the LLRF is substantiated in Chapter 8, where experimental results confirm that the LLRF output values are accurate to specific levels.

# **CHAPTER 2**

# **Cavity Parameters**

### 2.1 Description of the SRF

Superconducting RF cavities are used for producing the high cavity fields necessary for charged particle acceleration. An introduction to SRF cavities will be presented, and modeled, deriving the parameters to explain the behavior of low-level radio frequency (LLRF) disturbances imposed on the cavity. The goal is to present background material describing the problem and outlining the factors necessary to achieve the ultimate goal of controlling the cavity fields. The properties of a superconducting cavity are such that very high fields are obtained with relatively low power input. The unloaded Quality factor ( $Q_u$ ) for the MSU  $\beta = 0.47$  RIA prototype cavity is measured to be  $10^{10}$ , while operating at 805 MHz at  $2^{\circ}K$ . The resulting bandwidth is less than 1Hz (see equation (2.3)). This very narrow bandwidth means the cavity is sensitive to small vibrations or disturbances which physically change its shape, presenting the difficulty in maintaining the constant amplitude and phase required for a linear accelerator.

A linear accelerator or linac, is comprised of many cavities arranged for a straight line of flight beam of particles. The initial cavities are designed for a low  $\beta_o$ . In this  $\beta_o = \frac{v}{c}$ , where v is the speed of the particles and c is the speed of light. As the beam proceeds along the linac, the particles are accelerated and the  $\beta$  of the cavity msut be increased. To minimize costs, cavities are grouped in similar velocities, such that each group can accommodate a range of velocities. Identical cavities designed for an optimum  $\beta$  ( $\beta_{opt}$ ) is used for the entire group. The frequency of each group of cavities must be a harmonic of the initial cavity frequency. For example, MSU's RIA design includes an initial frequency in the low  $\beta$  cavities of 80.5 MHz, middle  $\beta$  cavities of 322 MHz and several high  $\beta$  groups of cavities operating at 805 MHz. These are the fourth and tenth harmonic frequencies of the initial 80.5 MHz.

Each cavity driving the linac must be synchronized to a common reference frequency so the beam is accelerated efficiently. The RF signal in the cavity is phase locked to this reference signal. The reference signal is designed to ensure the synchronization of the phase of all other cavities in the linac. Regardless of all exterior conditions, the cavity fields must ultimately remain phase locked and amplitude stable relative to a reference signal to maintain beam stability.

### 2.2 Circuit Model of the Cavity

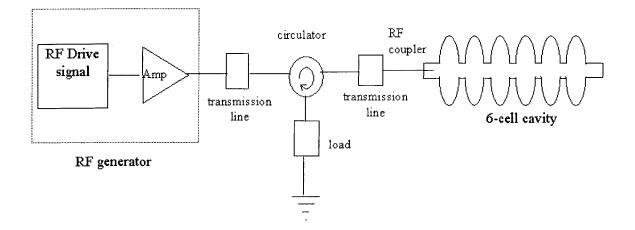

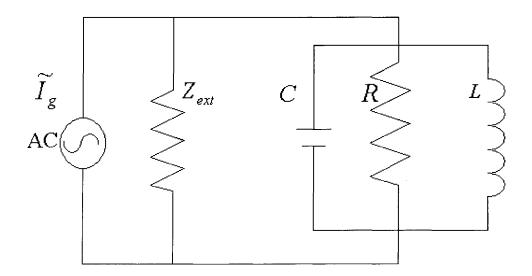

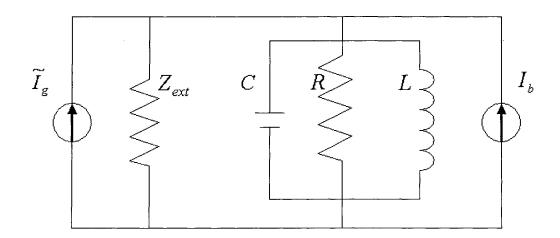

In order to show the effect of disturbances on the cavity, it is necessary to introduce variables that are relevant to the system. A useful means of describing the system is through a model of a resonant circuit. The overall system may be broken down into the cavity itself, a current source driving the system, a transmission line to feed the cavity, and a load. Figure 2.1 represents a schematic of a 6-cell cavity set-up. The load is the beam passing through the cavity absorbing energy as it is accelerated.

The current source is driven from an amplifier. The transmission line and the RF coupler feeding the resonator are designed to provide the power to the cavity. Since the cavity is overcoupled, to maintain stability, a circulator is necessary to ensure reflected signals do not saturate or damage the amplifier. The amplifier, circulator, coupler, and lines are lumped together as the Norton equivalent of the external current source consisting of the current source  $I_s$  and the shunt impedance  $Z_{ext}$ .

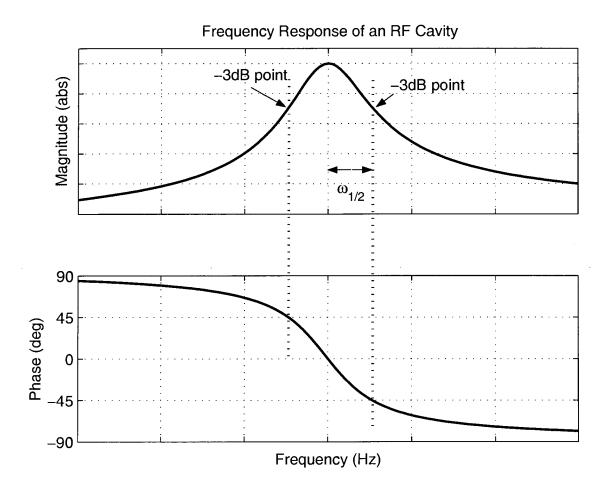

Resonating circuits or cavities act as a band pass filter and have a bode plot similar to that presented in figure 2.3. The ratio of the output signal relative to the input signal

Figure 2.1. General system set-up for a single 6-cell elliptical cavity.

Figure 2.2. Equivalent RLC circuit

is called the transfer function, and is presented in terms of the its magnitude and phase response. Here we can identify some fundamental aspects of the cavity response, which will be described in more detail later. The peak of the magnitude response is the resonant frequency  $\omega_o$ . The points at which we measure  $\frac{1}{2}$  the maximum power of  $\omega_0$  are labelled as the -3 dB points. The frequency between the -3db points is the bandwidth (*BW*) of the cavity and  $\omega_{\frac{1}{2}}$  is the  $\frac{1}{2}$  bandwidth.

$$BW = \omega_2 - \omega_1 \tag{2.1}$$

$$= 2\omega_{\frac{1}{2}} \tag{2.2}$$

where  $\omega_1$  is the lower -3dB frequency and  $\omega_2$  is the higher -3dB frequency. In (2.2), an even symmetric function about the center frequency  $\omega_o$ , is assumed.

The phase plot undergoes a 180 degree phase change over the frequency span of the resonator. Hence, the reactance of the circuit moves from an inductive circuit to a capacitive circuit through a frequency sweep, while the reactive components are equal at  $\omega_0$ . As the impedance is complex off-resonance, there is a phase difference between the voltage and current. At  $\omega_0$  the relative phase difference is 0, while at the -3dB points the phase is either  $\pm 45$  degrees.

The quality factor, or Q, of the cavity or resonator is defined by the magnitude response.

$$Q = \frac{\omega_0}{BW} \tag{2.3}$$

More specific equations of Q will be defined later in the chapter.

It is important to recognize that the equivalent circuit of the cavity is a reasonable representation of the cavity within the bandwidth of the cavity. Outside the bandwidth, the model illustrated in figure 2.2 does not normally hold.

Figure 2.3. Bode Plots.

### 2.3 **Resonator Description and Simplification**

Referring to the cavity as a RLC circuit implies that we are looking at a form of resonator, the simplest of which is a pillbox. Due to the symmetry of a pillbox resonator we can define the coordinate system in cylindrical coordinates, where z is the axis of symmetry, while the theta ( $\theta$ ) and rho ( $\rho$ ) components are symmetric about the z axis. For the pillbox, a TM<sub>010</sub> mode is present.

Figure 2.4. Cavity fields for  $TM_{010}$ .

A coupling probe induces fields in the cavity so that the electric field will propagate in the z direction. As the beam passes through the cavity in the z direction, it is accelerated by the electric field within the cavity, E(z,t).

$$E(z,t,\phi) = E(z)\cos(\omega t + \phi)$$

(2.4)

where  $\omega = 2\pi f$  of the RF frequency

The beam is made up of bunches or packets of charged particles, consisting of ions, electrons, or protons. E(z,t) is time varying and therefore, for the beam to obtain maximum

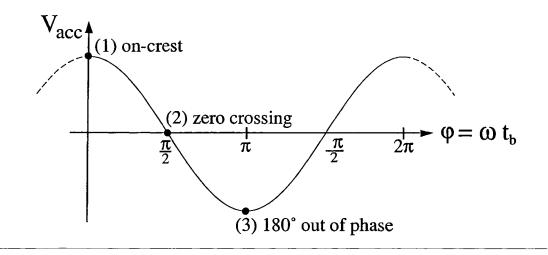

possible acceleration in the correct direction, the bunches must pass through the cavity while the electric field is at its maximum or "on-crest" (point 1 in figure 2.5).

Figure 2.5. Timing of the bunch.

We can define the phase delay as

$$\Psi = \omega t_b \tag{2.5}$$

where  $t_b$  is the particle injection time delay of the beam.

Figure 2.5 indicates that if the particles are injected with no delay, they are on crest. If the delay is  $\frac{\pi}{2}$  (point 2 on figure 2.5), there is no acceleration, while if the delay is  $\pi$  the bunch will be decelerated (point 3 in figure 2.5).

### 2.4 Beam Dynamics

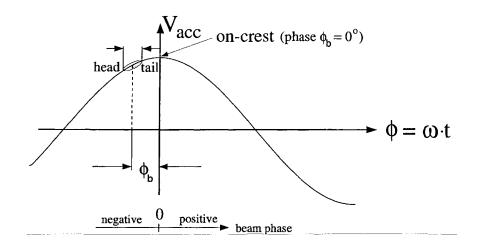

From beam dynamics, there is a desired value of phase offset to maintain or reduce the bunch size of each beam packet. A synchronous phase  $\phi_s$ , from the peak or crest, allows

bunches to remain tightly grouped. Slower particles obtain more energy, faster particle obtain less energy so the bunch remains in tight formation. This is known as the *second Robinson's stability criterion*.

Figure 2.6. Phase, i. e. synchronous phase  $\phi_s = \phi_b$ .

An important consideration here is the intended phase delay of the beam or phase delay in the cavity fields. There are desired set-points for the phase in individual cavities to ensure that beam particles accelerate as a bunch correctly.

Additionally, in an ideal linac, each progressive cavity would have an increasing  $\beta$  to account for the increasing speed of the beam. Cavity designs are shaped to match the frequency to the velocity of the particles and are referred to in terms of their  $\beta$ . In reality it is less costly to design a single cavity with an optimum  $\beta$  or  $\beta_{opt}$  to operate at a harmonic of the initial  $\beta$  frequency. Within a range of cavities of mutual design, the beam velocity will be too slow for the first cavity, appropriate for the middle cavity and too fast for the last cavity. By adjusting the phase set-points, a cavity can accommodate the beam with the most appropriate electric field to accelerate the beam efficiently. The amplitude and phase set-points of the cavity fields, are critical in terms of accelerating the beam.

### 2.5 Derivation of the Quality Factor

In the circuit model of figure 2.2, the resonance of the RLC circuit is defined as the frequency at which the inductive and capacitive reactance's are equal. This is given in terms of inductance (L) and a capacitance (C) as

$$\omega_o = \frac{1}{\sqrt{LC}} \tag{2.6}$$

The impedance of the parallel combination of inductor and capacitor at resonance is infinite, and all the generator current flows through the resistor (**R**) at this frequency. As noted earlier, as the cavity moves off resonance, either inductive or capacitive reactance exist in the circuit or cavity.

Comparing the circuit model to the cavity, the relationship of R in our model is relative to the resistive losses R on the walls of the cavity from surface currents induced by the electromagnetic fields. This value R is important in determining the power dissipated in the cavity. This is valuable in deriving the alternate definition of Q. In this case the unloaded Q or  $Q_u$  is defined as the ratio of stored energy (U), to energy ( $P_{cav}$ ) lost in one rf cycle (T). Where

$$P_{cav} = \frac{V_p^2}{2R} \cdot T \tag{2.7}$$

For the optimum cavity design where the beam  $\beta$  includes the cavity  $\beta_o$ , the ideal transit time for the particles corresponds to 180° of phase accumulation. In this scenario the particles are accelerated during the total time while exposed to the electric fields. Also at  $\beta_o$ ,  $V_{acc} = V_{cav}$ . The cavity potential is then

$$V_{cav} = \frac{2V_p}{\pi} \tag{2.8}$$

The accelerator community relates the cavity voltage to losses via  $R_{sh}$ , where  $R_{sh} = 2R$ ;

hence,

$$P_{diss} = \frac{V_{cav}^2}{R_{sh}} \tag{2.9}$$

and

$$Q_u = \frac{\omega U}{P_{cav}} \tag{2.10}$$

The time average stored energy at resonance is defined as the peak electric or magnetic field energy stored in the system. Alternatively, the time average stored energy can be in the capacitor and inductor used in the model of figure 2.2.

$$U = \frac{1}{2}\mu_0 \int_V |\mathbf{H}|^2 d\mathbf{v}$$

(2.11)

$$U = \frac{1}{2}LI_p^2 \tag{2.12}$$

$$U = \frac{1}{2} \varepsilon_0 \int_V |\mathbf{E}|^2 d\mathbf{v}$$

(2.13)

$$U = \frac{1}{2}CV_p^2 \tag{2.14}$$

By definition, at resonance the stored energy in the capacitor and inductor are equal; hence,

$$U = \frac{1}{2}CV_p^2 = \frac{1}{2}LI_p^2$$

$$Q_u = \frac{\omega U}{P_{cav}}$$

$$Q_u = \frac{\omega \frac{1}{2}CV_p^2}{\frac{1}{2}\frac{V_p^2}{R}}$$

$$Q_u = \omega RC \qquad (2.15)$$

From the circuit model, we derive this equation which will be used later to define the cavity tuning angle.

### **2.5.1** Additional Quality Factors of Interest

We have considered thus far the unloaded cavity; we can also derive the Q for other cavity conditions, such as when the beam passes through the cavity. We may do so by using the circuit model again, considering the external driving current  $\hat{I}_g$ , the external impedance  $z_{ext}$ , and a load. Our load is the beam passing through the cavity and represented by  $I_b$ . As the particles are accelerated they absorb energy from the cavity fields and must be represented by a load. The beam must be considered as part of the system, not as a simple resistive load but as a current load, due to the reactive components of the beam.

Figure 2.7. Equivalent RLC circuit with load.

The unloaded Q, as previously determined, was the ratio of stored energy to dissipated energy in the cavity. External Q ( $Q_{ext}$ ) is the ratio of energy stored in the cavity relative to the power dissipated in external devices from the cavity. This is given by,

$$Q_{ext} = \frac{\omega U}{P_{ext}} \tag{2.16}$$

while the loaded Q, which is the Q of the cavity with a beam passing through it, is given by

$$Q_l = \frac{\omega U}{P_{tot}} \tag{2.17}$$

where

$$P_{tot} = P_{cav} + P_{ext} \tag{2.18}$$

The loaded Q may be calculated as

$$\frac{1}{Q_l} = \frac{1}{Q_o} + \frac{1}{Q_{ext}}$$

(2.19)

We can describe the beam, by its own effective Q. Here the beam quality factor  $(Q_b)$  can be described as the ratio of stored energy in the cavity compared to the power delivered to the beam.

$$Q_b = \frac{\omega U}{P_{beam}} \tag{2.20}$$

In general the  $Q_{ext} \approx Q_l$ . As  $Q_o$  is typically orders of magnitude larger,  $Q_{ext}$  dictates the  $Q_l$ . This is because most of the power lost in the system is to the power coupler, transferring RF power to the cavity. By increasing the coupling, or overcoupling the cavity with power, more power is lost in the coupler further reducing the  $Q_{ext}$  and  $Q_l$ . The lower  $Q_l$  broadens the bandwidth of the system making it less susceptible to amplitude and phase offset from shifting resonant frequencies.

### 2.6 **Tuning Angle and Cavity Voltage Requirements**

The circuit model in figure 2.7 considered the effective generator current  $I_g$  and the beam load as a current  $I_b$ . Both  $I_g$  and  $I_b$  are sinusoidal and of the same frequency. The phase

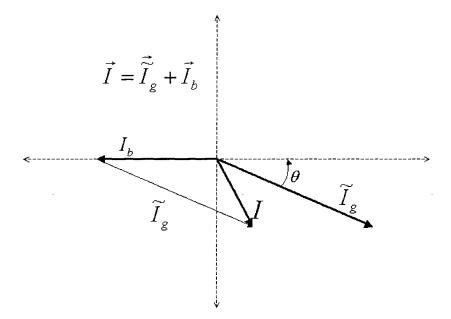

difference between these two currents is represented as  $\theta$  in figure 2.8. The timing of beam injection relative to the reference signal synchronizing all the cavities can control this phase angle  $\theta$ . If we combine the two parallel currents into a single source *I* and analyze the circuit we will determine the steady state solution of the cavity voltage. This combined current is given by

$$I = \tilde{I}_g + I_b \tag{2.21}$$

Figure 2.8. I representing generater and beam currents

Using Kirckoff's current law we know that

$$I = I_R + I_L + I_C \tag{2.22}$$

and

$$I = \frac{V_c}{R} + \frac{1}{L} \int_0^t V_c dt + \frac{CdV_c}{dt}$$

(2.23)

By differentiating both sides of (2.23), we find

$$\frac{dI}{dt} = \frac{1}{R}\frac{dV_c}{dt} + \frac{1}{L}V_c + \frac{Cd^2V_c}{dt^2}$$

(2.24)

and divide by *C*, we have

$$\frac{1}{C}\frac{dI}{dt} = \frac{1}{RC}\frac{dV_c}{dt} + \frac{1}{LC}V_c + \frac{d^2V_c}{dt^2}$$

(2.25)

This second-order differential equation represents the cavity voltage driven by the amplifier, accelerating the beam.

Let the applied current be

$$I = I_o sin(\omega t) \tag{2.26}$$

The steady state solution of the differential in (2.25) equation will be given by

$$V_{cav} = V_c \sin(\omega t + \psi) \tag{2.27}$$

Utilizing (2.26) and (2.27) in (2.25) and comparing both sides of the equation for  $\sin(\omega t + \psi)$  as well as  $\cos(\omega t + \psi)$ , we can find the equations solution,

$$\tan \Psi = R_l (\frac{1}{\omega L} - \omega C) \tag{2.28}$$

where the beam load included in  $R_l$ ,

$$V_{c} = \frac{R_{l}I}{\sqrt{1 + [R_{l}(\frac{1}{\omega L} - \omega C)]^{2}}}$$

(2.29)

The angle  $\psi$  is the phase angle between the generated current and the generated voltage, or between the beam current and beam voltage. This is known as the cavity-tuning angle.

$$\tan \Psi = R_l \frac{C}{\omega} (\frac{1}{LC} - \omega^2)$$

(2.30)

$$= \frac{R_l C}{\omega} (\omega_0^2 - \omega^2)$$

(2.31)

$$= \frac{R_l C}{\omega} [(\omega_0 + \omega)(\omega_0 - \omega)]$$

(2.32)

$$\cong \frac{R_l C}{\omega} \cdot 2\omega \Delta \omega \tag{2.33}$$

Where  $\triangle \omega$  is the difference between the driving frequency  $\omega$  and the cavity frequency  $\omega_o$ . If  $\triangle \omega$  is small, than  $\psi$  may be used in the approximation (2.33).

Alternatively given (2.15)

$$\tan \Psi = \frac{2Q_l \Delta \omega}{\omega} \tag{2.34}$$

Finally

$$\tan \psi \approx 2Q_l \frac{\Delta \omega}{\omega} = 2Q_l \frac{\Delta f}{f}$$

(2.35)

and

$$V_c \approx \frac{R_l I}{\sqrt{1 + \tan^2 \psi}} \tag{2.36}$$

Graphing this  $V_c$  versus frequency verifies the fundamental cavity responses mentioned earlier, as seen in figure 2.3. The bandwidth of the loaded system is noted by the points where the voltage drops to  $\frac{1}{\sqrt{2}}$  of the voltage or the -3dB value of the maximum voltage, or the stored energy drops to  $\frac{1}{2}$ . The -3dB occurs when the angle is  $\frac{\pi}{4}$  which equates to  $\frac{1}{\sqrt{2}}R_lI$  when used in equation (2.36).

### 2.7 Controlling Bandwidth

Understanding the relationship of the various Q's (especially that of  $Q_b$  of the cavity to the bandwidth) is essential in designing the power requirements necessary to obtain and control the desired cavity fields. As mentioned earlier, very high Q factors relate to very narrow bandwidth and therefore a very sensitive environment. Any noise or low level disturbance will de-tune the resonant frequency. Once the  $\omega_0$  of the cavity does not agree with the RF drive frequency, which is governed by a reference signal throughout the linac, the cavity fields will drop in amplitude and will deviate from the desired phase set-point.

Existing high velocity accelerators have usually had high beam currents. The high beam current relates to a low  $Q_b$ . The low  $Q_b$  reduces the overall  $Q_l$ , which in turn increases the bandwidth of the cavity. Microphonic induced frequency variations become relatively insignificant to the loaded bandwidth, creating small amplitude variation in the system, and the majority of RF power provided is transferred to the beam. Disturbances in the form of microphonics have little effect on the phase and amplitude of the system when the  $\Delta \omega$  is considerably less than the cavity bandwidth.

RIA has a low beam current and therefore has a high  $Q_b$ . The overall loaded  $Q_l$  of the system will remain very high, resulting in cavity field control dominating the power requirements in the presence of microphonic disturbances.

#### 2.7.1 Calculate the Power Requirements for Detuning

With some form of amplitude and phase control, there is still a maximum amount of power that may be available to adjust for resonant frequency offset. Hence, the maximum amount of detuning possible can be calculated for a given amount of power generated.

RIA beam currents are designed to be relatively low at 0.328 mA. The amount of power

required to sustain the field in the cavities has been designed to be at a level where the delivered or coupled power level is twice that of the required beam loading power.

In deriving the equations to determine the control bandwidth, let  $P_{bd}$  be the beam design power and  $P_b$  be the power of the beam.

$$P_g = \frac{P_{bd}}{4} \left[ \left( 1 + \frac{P_b}{P_{bd}} \right)^2 + 4 \left( \frac{\delta \omega}{\Delta \Omega} \right)^2 \right]$$

(2.37)

where

$$\Delta \Omega = BW = \frac{\omega_0}{Q_l} \tag{2.38}$$

$$Q_l = \frac{\omega U}{P_{bd}}$$

(2.39)

$$Q_b = \frac{\omega U}{P_b} \tag{2.40}$$

$$\frac{Q_l}{Q_b} = \frac{P_b}{P_{bd}} \tag{2.41}$$

$$Q_b = \frac{\omega_0}{BW_b} \tag{2.42}$$

$$\omega_0 = Q_b B W_b \tag{2.43}$$

$$BW = 2\omega_{\frac{1}{2}} \tag{2.44}$$

$$\omega_0 = 2Q_b \omega_{\frac{1}{2}b} \tag{2.45}$$

Using (2.41) and (2.39) in (2.37) and dividing by  $P_b$ , we get

$$\frac{P_g}{P_b} = \frac{P_{bd}}{4P_b} \left[ \left( 1 + \frac{P_b}{P_{bd}} \right)^2 + 4 \left( \frac{\delta \omega Q_l}{\omega_0} \right)^2 \right]$$

(2.46)

Substituting (2.41) and (2.43) into (2.46)

$$\frac{P_g}{P_b} = \frac{Q_b}{4Q_l} \left[ \left( 1 + \frac{Q_l}{Q_b} \right)^2 + 4 \left( \frac{\delta \omega Q_l}{BW_b Q_b} \right)^2 \right]$$

(2.47)

If we assume that

$$Q_{ext} \approx Q_l \tag{2.48}$$

then

$$\frac{P_g}{P_b} = \frac{Q_b}{4Q_l} \left[ \left( 1 + \frac{Q_l}{Q_b} \right)^2 + \left( \frac{\delta \omega Q_l}{\omega_{\frac{1}{2}b} Q_b} \right)^2 \right]$$

(2.49)

By rearranging (2.47) so that its derivative with respect to  $\frac{Q_l}{Q_b}$  and evaluating it at 0, we find the maximum ratio of  $Q_{ext}$  to  $Q_b$ . Assuming the overall generator power to be twice the beam power, the maximum ratio of  $\frac{Q_l}{Q_b}$  calculates to be 0.33. Using this in (2.47) to determine the maximum allowable detuning, to occur, while maintaining control of amplitude and phase, calculates to 5.68 of the beam BW from equation (2.42). The system can maintain control even if microphonics detunes the system 5.68 times the beam bandwidth, under these conditions.

### 2.8 Graphically Demonstrate Loss of Resonance

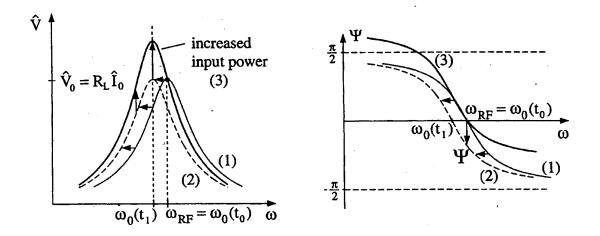

The left graph of figure 2.9 is the magnitude response of a cavity where the cavity resonance frequency ( $\omega_{RF}$ ) occurs at the peak voltage of the initial curve (line 1) at t = 0. The required voltage at resonance is indicated by a dot. Line 2 represents a shift in frequency due to some disturbance where the new resonant frequency is established at  $\omega_o$  at time  $t_1$ . To compensate for the drop in voltage at the cavity resonance frequency due to the shift, an increase in power is necessary (line 3) to maintain the proper cavity fields at the resonant frequency  $\omega_0$ .

Similarly, the phase plots on the right represent the shift in phase due to the disturbance represented by lines 1 to 2. Corresponding phase compensation is also necessary to bring

Figure 2.9. Effects of disturbance on resonant frequency.

the phase of the cavity back in line with the reference signal.

## 2.9 Conclusion

We have introduced a number of factors relative to Superconducting Radio Frequency cavity dynamics and have established the relationship between the cavity parameters, bandwidth and quality factors of the cavity. For more detailed review of cavity parameters and beam dynamics, the interested reader is referred to [2].

The Q factors of the cavity play a significant role in that the amount of over-coupling determines the loaded Q. The loaded Q dictates the performance of the cavity and its sensitivity to disturbances. Efficient beam acceleration is possible only if cavity fields are steady and phase locked to a reference signal synchronizing the entire linac. Ultimately, a form of control is necessary to regulate the phase and amplitude of the cavity fields in a manner such that the desired phase and amplitude may be established and maintained to a specific accuracy.

# **CHAPTER 3**

# **Mitigation of Disturbances**

### 3.1 Disturbances

With a background regarding cavity dynamics and an understanding of the control parameters of the cavity, the source of disturbances and methods of controlling them can now be described. There exists both mechanical and electrical methods of dealing with these disturbances. Mechanical methods mitigating dealing with disturbances are capable of reducing the level of disturbance to a workable range, but not eliminating them completely. This chapter describes general mechanical and electrical methods to virtually eliminate the disturbance.

Microphonics is the definition of low level disturbances which affect the cavity. In the case of the RIA high  $\beta$  cavities, which are the most sensitive cavities, it has been determined that most frequencies over 300 Hz may be neglected due to their insignificant effect on the cavity.

Microphonics are mechanical vibrations from the surrounding environment. The cavity is connected directly and indirectly to cryogenic lines, pumps, other plumbing, and to the building floor itself. Motors, equipment, even ground vibrations from road traffic may be considered sources of vibrations. There are a multitude of synchronous machines in our environment, vibrating at approximately 60 Hz and harmonics of 60Hz. As our environment is surrounded by sources of vibrations, managing the disturbances is critical to maintain stable cavity fields.

### **3.2** Mechanically Dealing with Disturbances

The simplest method of damping any vibrations would be to isolate and even remove the source of the vibrations permanently. Locating cavities in an isolated environment away from motors, traffic and other vibrating sources will help, but there are numerous connections that cannot be completely isolated. Cryogenic feed lines, necessary to maintain superconductivity, may be damped so as to reduce the vibration from pumps and motors, but can not be eliminated. Reducing the amount of physical vibration within proximity of the cavity will help reduce the amount of detuning.

Mechanically damping the vibrations is possible by stiffening parts of the cavity. By increasing the mechanical stiffness of the cavity by welding support struts, we increase the stiffness K matrix, thereby increasing the natural resonant frequency of the parts themselves. The forced response of the cavity due to a disturbance will be of a higher frequency, which may be out the susceptible range of problematic frequencies, or in the high  $\beta$  cavities  $\omega_{dis} > 300$ Hz.

The critical component for reducing vibrations in the cavity mechanically, is the tuner. A tuning arm connected directly to the SRF cavity, mechanically alters the length and shape of the cavity thereby changing the resonant frequency of the cavity. A piezoelectric actuator activated by a controller can be use as a means for compensating microphonic vibrations, by applying an equivalent disturbance with the reverse phase [8]. The reduction in mechanical vibration will bring down the disturbance to within the BW, so it may be controlled electrically. Additionally, it will reduce the RF power requirements necessary to phase stabilize the cavity.

#### 3.2.1 Overcoupling

We have described the relationship between the  $Q_l$  of the cavity and its bandwidth. If the cavity has a lower  $Q_l$  due the over-coupling of the cavity, the overall bandwidth is increased.

If the BW of the system is large enough, then small variations in the resonant frequency (i. e. microphonics) will have little affect on the cavity fields.

In order to over-couple the cavity it is necessary to increase the power delivered by the source. The amount of RF power required for over-coupling is dependent on beam loading and the amplitude of the induced noise, and can determined through testing in a realistic environment. This higher power increases the loaded Q and broadens the BW of the system, allowing for phase stabilization. Aside from various methods of mechanical, and digital control, this has historically been an effective method of handling microphonics.

#### **3.2.2 Reactive Tuning**

ATLAS, the heavy ion accelerator at Argonne National Labs, use a reactive tuner to control microphonics. The idea is based on controlling the reactive component of the detuning field. A circuit made of diode switches, fast switches the load impedance of the reactive power stored in the transmission line, coupled to the cavity, to compensate for the detuning. This method has been used to phase stabilize cavities of 48–150 MHz at ATLAS, and has proved to be an effective and stable system with numerous hours of operation. The system has not been effectively used on higher frequency systems.

#### **3.2.3 Changing the Resonant Frequency**

The tuner mechanically changes the  $\omega_o$  of the cavity is a method of adjusting the resonant frequency. Another method of adjusting for the shifting resonant frequency, is by allowing the driving frequency of the cavity to shift with the changing resonant frequency. This can be accomplish by means of modulating or adjusting the RF signal driving the system.

We shall consider two methods of generating the driving RF signal, the self excited loop, and the generator driven control loop. The former system has the ability to shift its resonant frequency while the latter is based on a fixed known frequency.

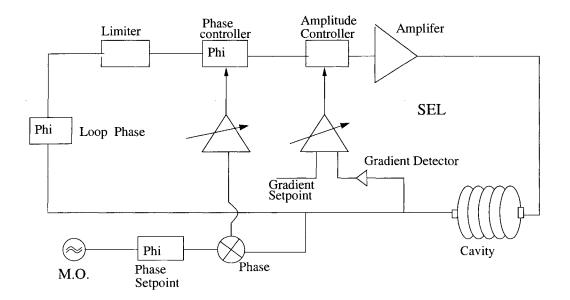

#### Self excited system

In the self excited loop, the signal from the cavity output is compared to the driving RF signal. The two signals are processed by a mixer where the RF and LO signals are of the same frequency. The filtered IF is the instantaneous phase difference between the two signals. This measured phase difference has a direct relationship to the frequency offset by equation (3.1). By applying this phase difference to the signal generator in the form of a modulation, the driving signal can be adjusted for the difference just measured. The drive signal moves in relation to the resonant frequency of the cavity thereby allowing for constant fields within the cavity.

Figure 3.1. Self Excited Loop

$$\frac{d\omega}{dt} = \phi \tag{3.1}$$

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### **Generator driven**

The second means of driving the system is through generator driven loop, which is based on a fixed frequency and operates under the assumption that the cavity is at a fixed resonance. Any offset from resonance will have to be adjusted elsewhere. The controller procured by NSCL and under consideration for this thesis is a generator driven system. We will refer to the controller as the LLRF controller.

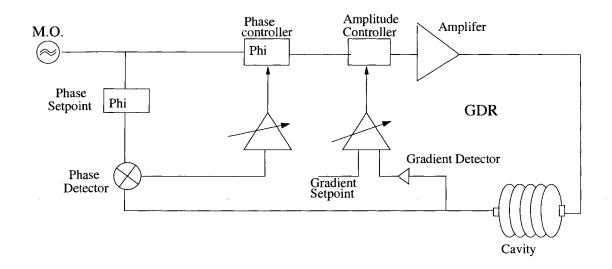

Figure 3.2. Generator Driven Loop

#### **3.2.4 Digital Control**

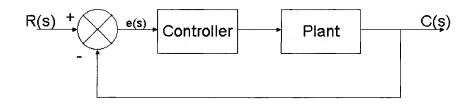

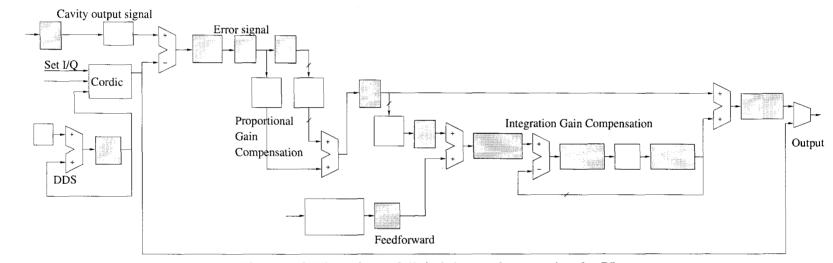

While diminishing the disturbances, mechanical methods cannot over-come the very narrow bandwidth of high Q superconducting cavities to maintain resonance. The digitization and re-creation of the RF drive signal back to an analog signal allows for discrete analysis and correction of the driving signal. The speed at which digital systems operate makes a disturbance under 300 Hz appear relatively slow. This is accomplished by electrically correcting the signal, by point-by-point adjustment of the signal using a Proportional Integrating (PI) control loop to keep values at their desired set-points. This control system will fit in with a generator driven control system so that the resonance of the cavity is maintained as well as the cavity fields.

#### **Digital Signal Processing**

One method of digital control is through the use of a Digital Signal Processor (DSP). The DSP is capable of manipulating digital data by analyzing and modulating signals in real time. In this case, it would alter or adapt the values necessary to ensure the RF drive signal is at its proper frequency. DSP's have been used at numerous facilities around the world; for example, the Telsa Test Facility have used DSPs for systems operating at 1.3GHz for a pulsed beam. Pulsed beams are considerable more complicated in that there are Lorentz forces present. Each pulse induces a new electric field, magnetically altering the shape of the cavity and changing the resonant frequency at each pulse. Positive aspects of DSPs are that they are relatively easy to program and available through several manufacturers.

#### Field Programmable Gate Array

Another processor, which is commonly used in telecommunications, is a Field Programmable Gate Array (FPGA) chip. Similar to Programmable Logic Chip (PLC), the FPGA is made up of thousands of logic units. The benefits of using a FPGA, are its high speed throughput and parallel processing capabilities that allow for real time processing, as well as its ability to be reprogrammed along with its cost. It may be programmed to do similar functions as a processor chip may do, but does not have the overhead architecture. A simple logic output may take ten times longer to process on the processor because of its overhead, but the FPGA is limited to less complicated math operations, because it lacks some of the necessary overhead. The number of operations per sample is much higher with FPGA due to its architecture, accounting for its speed [11].

The FPGA is faster when complicated co-processing procedures are not required, in

which case a DSP is faster. For example, a trigonometric calculation is faster on a DSP compared to an FPGA, unless a form of digital manipulation of shifting registers to multiply and process numbers is used in the FPGA code. Using a routine called Cordic, one can determine the phase and magnitude of a signal without using a single trigonometric function.

FPGA's are faster in terms of raw performance but there are downsides as well. An FPGA is much more complicated to program. There are limited number of qualified programmers with the skill set for Verilog or VHDL. Due to the complexity of the FPGA, the manpower and implementation costs are disadvantageous for most small applications. Newer FPGA chips have DSP functionality built in, allowing for some more complicated processing. The LLRF controller referred to in this thesis is based on the FPGA chip.

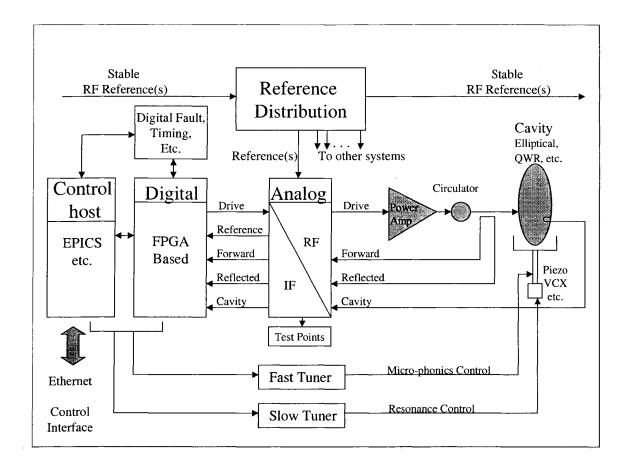

### **3.3 Digital Controls Within the Linac**

A generic method of how a controller would fit into the overall linac is described in figure 3.3. This is a representation of a single cavity control. Each cavity would have the similar set-up, operating at the appropriate frequencies. The reference distribution at the top is distributed throughout the linac and must be extremely stable in phase. The entire system is dependent on the phase stability of this reference signal. The right side of the figure displays the cavity, amplifier and measured signal from the system. The piezoelectric actuator is connected to the tuner to mechanically control vibrations. The control for the actuator is in the form of a fast and slow tuner from the main controller.

We define fast tuning as the signal applied to the tuner to reduce vibrations under 300 Hz. In this case, the LLRF controller is the tool to measure the change in frequency and or phase, while a separate controller, such as an Adaptive Feed-forward Controller (AFC) may be implemented, to mechanically dampen cyclical sinusoidal disturbances [8].

Slow tuners will be in the form of screw type device, stepper motor or prestressing the

Figure 3.3. System diagram.

piezoelectric actuator to handle tuning or very slow drifts in frequency. Again the control will be dictated from the main controller which monitors all system parameters.

The left side of the figure contains the control host and the digital controller. The control host is the interface that handles the user interface and communicates directly with the digital controller. Experimental Physics Industrial Controls Systems (EPICS) is a well known system used in most accelerator labs, to interface with, monitor and control sensors as well as motors throughout the entire accelerator.

The digital controller is where the analog signals are digitized, measured and processed to create the corrected new output driving signal to the cavity. The controller will be described in detail in chapter 5.

In the middle of the figure is the analog converter. It splits and downconverts the mea-

sured signals from the cavity to the appropriate intermediate frequency (IF) and amplitude that the digital controller can handle. Test points allow verification of the signals at the IF and RF levels.

This arrangement is not specific to any one type of digital controller. In our case, it suitably represents how the controller ties into the overall system.

## 3.4 Reasons for Choosing LBNL LLRF Controller

We procured the LLRF controller from Lawrence Berkeley National Labs (LBNL) as this design was tested and being commissioned for use at Spallation Neutron Source (SNS) accelerator, in in Oak Ridge, Tennessee. While their system is pulsed, and RIA is continuous wave (CW), its complexity would likely be able to support RIA specifications. Dr. Larry Doolittle who put together the LLRF controller has a wealth of experience in the field accelerator physics and microphonic detuning. Additionally, LBNL was willing to support outside labs, making their controller the only system of its type available.

It would appear that this design would have the best chance of success, given the background and the lessons that we could learn from the installation and commissioning at SNS.

## 3.5 Conclusion

By understanding the source of disturbance and several methods of reducing or eliminating them, we can look at one specific type of controller that shows promise in stabilizing cavity fields. The digital controller, specifically the LBNL LLRF controller, will be discussed in its method of operation. We have seen a glimpse of how the controller ties in to the system. Further discussion of signal processing will help in understanding the method this controller operates.

# **CHAPTER 4**

# Signal Capture

### 4.1 Introduction

Having decided on a digital controller to stabilize cavity fields, a basic understanding of various components and signal processing tools is necessary to discuss some of the methods used in the LLRF controller. A brief discussion of mixers, downconversion, and sampling rates will be described.

## 4.2 Vector Control

If we consider the two methods discussed in 3.2.3 of how to drive the cavity, both the generator driven and self-excited system rely on measurements of the cavity field amplitude and phase. Cavity voltages can be expressed as vectors in the complex plane, and may be described either in terms of amplitude and phase in polar coordinates, or as real and imaginary components in rectangular coordinates.

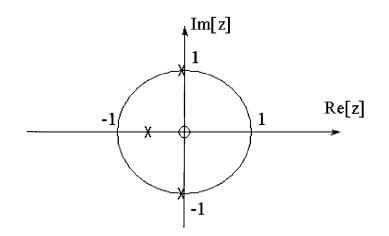

Real and imaginary components are sometimes referred to as I (in phase  $0^{\circ}$ ) and Q (quadrature  $90^{\circ}$ ). Analog components such as IQ demodulators are capable of extracting information such as phase modulation or frequency offset from center frequency. Alternatively, the I and Q values may be extracted digitally using analog-to-digital converters (ADC). In analyzing control systems for large disturbances, a vector controller based on real and imaginary components is preferable. A phase controller could possibly correct the phase into the wrong quadrant due to the cyclic periodicity of phase response, as informa-

tion is based on phase location only. A change of  $30^{\circ}$  from  $0^{\circ}$  may be in the first or forth quadrant. Its relation to a previous input may not account for a three quadrant shift in phase. The phase appear to be the same but the direction of the change is not the same, and the compensation would not be correct, if based on the incorrect phase position. In complex form the exact position is known relative to a previous point. The LLRF controller uses a digital method to obtain I and Q signal information.

#### 4.3 Downconversion

The RIA cavity tested for this report operates at 805 MHz. Even as technology improves, the fastest commercially available ADC today, can sample at 105 MHz. It is therefore necessary to downconvert the high frequency signal to a lower frequency that the ADC can handle. Choosing the appropriate frequency depends on the ADC sample rate, as well as other issues such as imaging. Image frequencies are repetitions of a frequency spectrum, resulting from discreet sampling.

Downconverting is performed through the use of mixers. A mixer is essentially a signal multiplier of two input signals, a radio frequency (RF) signal and a local operator (LO) signal. The output is an intermediate frequency (IF) which is the sum and difference of the two frequencies. Filtering out the unwanted frequency and harmonics will leave an IF of a specific frequency. The trigonometric function (4.1) may be evaluated by applying two separate signals A (4.2) and B (4.3),

$$\sin x \sin y = \frac{1}{2} \left[ \cos \left( x - y \right) - \cos \left( x + y \right) \right]$$

(4.1)

We refer to A as,

$$a(t) = A\sin[(\omega_a t) + \theta_a]$$

(4.2)

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

and B as,

$$b(t) = B\sin[(\omega_b t) + \theta_b]$$

(4.3)

Multiplying these two signals, the output becomes,

$$a(t)b(t) = \frac{AB}{2} [\cos(\omega_a - \omega_b)t + (\theta_a - \theta_b)] - \frac{AB}{2} [\cos(\omega_a + \omega_b)t + (\theta_a + \theta_b)]$$

(4.4)

The result is the sum and difference of frequencies A and B, as shown in (4.4). If for example A operated at 100 MHz and B at 10 MHz the IF would be both 90 MHz and 110 MHz. Adding a low pass filter would leave the 90 MHz signal to work with. This is the basis for modulating and demodulating signals. While these equations are true for ideal components, in reality there are some non-linear responses at higher amplitudes and image frequencies that may add some distortion or noise into the system.

Noise, or unwanted signals can emerge from mixers in the form of harmonics from the original signal or internally from the switching action of the mixer itself. Double balanced mixers (DBM) have the ability to avoid spurious noise on the IF port due to its construction. A diode ring completely isolates the IF from the RF and the LO. Equation (4.5) calculates the IF frequency for all possible harmonics of the input signals. An ideal DBM rejects all spurious responses when either or both input harmonics are even (m and/or n are even). For this reason, DBMs are a preferred mixer. Various combinations of integer multiples of either or both the RF and LO can emanate from the mixer. It is therefore necessary to consider the possible combinations of the sum of multiples of each frequency as an image frequency.

$$\omega_{IF} = \pm m\omega_{RF} \pm n\omega_{LO} \tag{4.5}$$

Note that m and n are integer harmonics of both RF and LO that mix to create spurious products. In reality the amplitude of the spurious components decrease in amplitude as the value of m or n increase, so higher-order multiples cause minor distortion relative to the first harmonic and are typically filtered out.

Looking back at our example, the first image occurs when the 2nd harmonic of B mixes with A, resulting in  $\pm 20$  MHz from the 100 MHz. DBMs reduce this even harmonic so we can neglect it and consider the  $3^{rd}$  harmonic which produces a disturbance out of range. The  $2^{nd}$  harmonic of A (200 MHz) and  $9^{th}$  harmonic of B (90 MHz) result in images at 110 MHz and 290 MHz. At issue is when our desired IF is 110MHz and an image occurs at that same frequency. The amplitude readings for the IF signal would sum the two signals resulting in incorrect measurements. The amplitude of the  $9^{th}$  harmonic may cause problems depending on the sensitivity of the system.

Another issue is phase noise, which is the result of an unstable LO, or a clock with jitter. An unstable reference clock has some shift in time. Any movement in time is relative to a phase shift and will be seen at the output as jitter in amplitude or phase. Clock drift sometimes occurs as environmental changes occur that would also affect measurements. To compensate or correct for drift in clock cycles in our cavity set up, a reference signal is used to phase match all cavities in the linac. The controller uses the reference signal to phase lock the cavity signal. By phase locking the cavity signal the frequency is kept in complete synchronization in phase and therefore the amplitude is also matched in terms of clock cycles. Phase locking the signals ensures that the sampling frequency is correct and avoids sampling uncertainties.

In the case of the 805 MHz cavity, 50 MHz is the IF frequency. The LO frequency was decided to be 755 MHz. The IF is far enough from both the RF and LO to easily filter out any sideband or images that might appear as a result of the mixer.

38

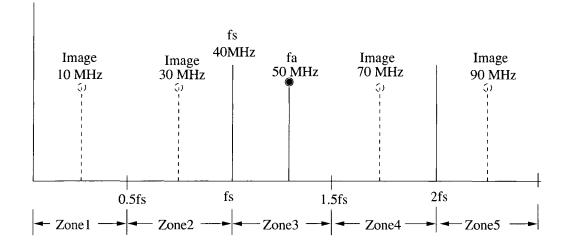

### 4.4 Digital Sampling

Sampling acquires waveform representation through a sequence of discrete values of a continuous time signal taken at uniform time intervals. Each discrete value is a measurement of the waveform amplitude at its sample time. Resulting in a sequence of numbers representing amplitude at even timed intervals. The inverse interval period, or sampling frequency  $(f_s)$ , is usually required to be a minimum of twice that of the maximum frequency in question  $(f_a)$ , to obtain sufficient data to reconstruct the original signal with no loss of information. Images or aliases may still exist after sampling, depending on the sampling frequency, therefor some care must be taken in the design to avoid noise.

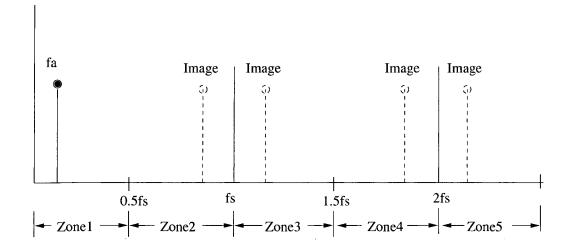

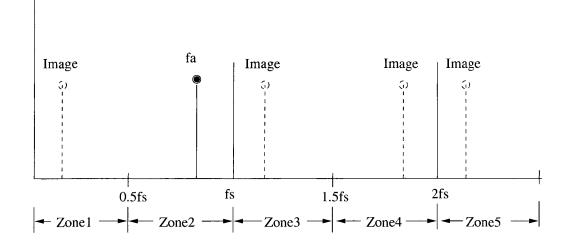

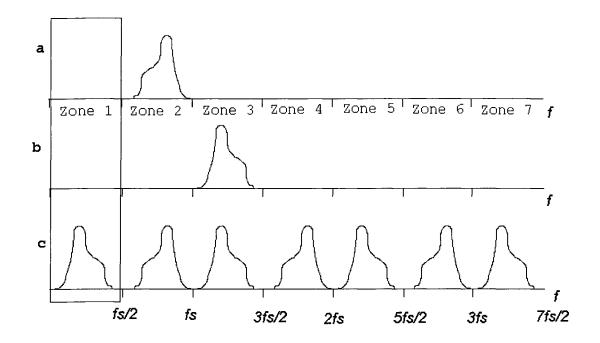

#### Nyquist zones

The first Nyquist zone is defined as the range of frequencies between DC and  $\frac{f_s}{2}$ . The frequency spectrum is divided into infinite Nyquist zones. The 1<sup>st</sup> Nyquist zone starts at DC, the 2<sup>nd</sup> Nyquist zone starts at  $\frac{f_s}{2}$ , the 3<sup>rd</sup> zone starts as  $f_s$ , and continues on, as can be seen if figure 4.2.

The sampling frequency must adhere to the Nyquist bandwidth to avoid aliasing. Nyquist Bandwidth states that the sampling frequency must be greater than twice the frequency spectrum bandwidth of the input signal in order to be able to reconstruct the original signal perfectly from the sampled version. If a signal has a center frequency of 805 MHz,  $\pm 1$  MHz, then the spectrum BW is 2 MHz and the minimum sampling frequency would be 4 MHz after downconversion. Images of the original signal occur at integer multiples of the sampling frequency.  $|\pm m f_s \pm f_a|$

where m = 1, 2, 3, ...

Looking at figure 4.1, we can see the frequency domain representation of  $f_s$ ,  $f_a$ , and the alias frequencies of the original signal.

$f_s$  = Samplingfrequency

$f_a$  = Frequencyspectrumofinterest

Figure 4.1. Signal  $f_a$  sampled at  $f_s$  using ideal sampler with images at  $|\pm m f_s \pm f_a|, m = 1, 2, 3, ...$

Figure 4.2, shows that if  $f_s$  is too close to  $f_a$ , an image frequency is produced in the 1<sup>st</sup> Nyquist zone. Note that if we consider the condition of figure 4.2 where a potential noise (unwanted signals) exits at any of labeled image frequencies, there will be an image of that particular noise in the 1<sup>st</sup> Nyquist zone. In this case the noise will be sampled as well as the intended signal. To avoid any spurious frequency components in the 1<sup>st</sup> Nyquist zone, appropriate filtering is required on the analog signal prior to the ADC. A well designed 'anti-aliasing filter' will avoid any spurious signals outside the Nyquist bandwidth. This will be even more important when we discuss undersampling techniques.

Just as in analog demodulation, a  $f_s$  too close to  $2f_a$  makes it more difficult to filter away unwanted images, due to limitations on the spectral sharpness of the response filter. By

Figure 4.2. Sampling a signal outside the first Nyquist zone, image falls within the first Nyquist zone.

increasing the sampling rate, the anti-aliasing filter roll-off requirements may be lowered. Of course, there are limitations on how fast ADCs can sample, and inherently the cost is reflected in the speed.

Baseband sampling occurs when all signals of interest are within the 1<sup>st</sup> Nyquist zone. With baseband signals all the images occur outside the 1<sup>st</sup> Nyquist zone. Undersampling or harmonic sampling occurs while sampling a  $f_s$  higher than the 1<sup>st</sup> Nyquist zone.

#### Undersampling

Observing the sampled data spectrum of a frequency in the second Nyquist zone reveals output identical, yet frequency reversed relative to the baseband frequency (figure 4.3). The original spectrum is folded in the second Nyquist zone and then again for the third Nyquist zone, and continues folding in each zone. Exact data representation may be acquired from a signal from any odd Nyquist zone, given the signal with the Nyquist bandwidth. This limitation is known as the *Nyquist critea*. Otherwise stated as *a signal must be sampled at a rate equal to or greater than twice its bandwidth in order to preserve all the signal information*.

Figure 4.3. Undersampling a signal in second and third Nyquist zone resulting in identical sampled data spectrum.

Figure 4.3, plot **a**, is an example of a signal whose frequency spectrum resides in the  $2^{nd}$  Nyquist zone, and plot **c** is the resulting frequency spectrum. Plot **b**, is the reversed frequency spectrum of plot **a** and sits in the  $3^{rd}$  Nyquist zone. The output from plot **b**, also results in the equivalent frequency spectrum plot **c**. Note how the even zones have a reversed frequency spectrum, and that the sampled signal is clearly within the Nyquist bandwidth, and therefore not aliased.

Any additional signals or noise outside the original Nyquist bandwidth will create images in all other zones, producing noise or a corrupted frequency spectrum within the sampled data. For under-sampling techniques, the anti-aliasing filter prior to the ADC needs to be a bandpass filter with high roll off to ensure a clean sampled spectrum of the original signal, by confining the sampled frequency to the Nyquist bandwidth.

## 4.5 Demodulation

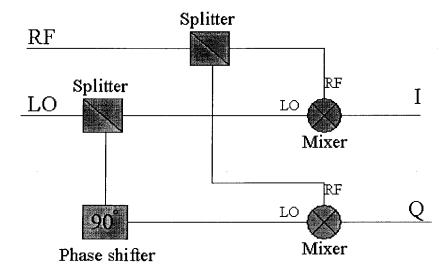

#### 4.5.1 Analog

Traditional analog I/Q demodulators require the RF signals to be split and compared to a LO to determine I and Q, through the use of mixers. The filtered output of the LO and RF signal is I, while Q is the filtered output of RF mixed with LO phase shifted 90°. The values of both I and Q are then sampled by an ADC and digitized to obtain the digital version.

Figure 4.4. Analog method of determining I and Q values.

Areas of difficulty with analog IQ demodulation arise from any gain or difference in signal amplitudes, or phase errors to mixer inputs. Mixers inputs must have identical amplitude inputs for both I and Q measurements. The phase separation for the LO must be exactly 90°, for true Q values. Physical issues such as cable lengths for phase matching, amplitude gains, leakage through any mixer ports, DC offsets, as well as impedance matching components are all potential sources of error. These errors may be eliminated or compensated for by careful RF design, but any single error may cause RF measurement errors.

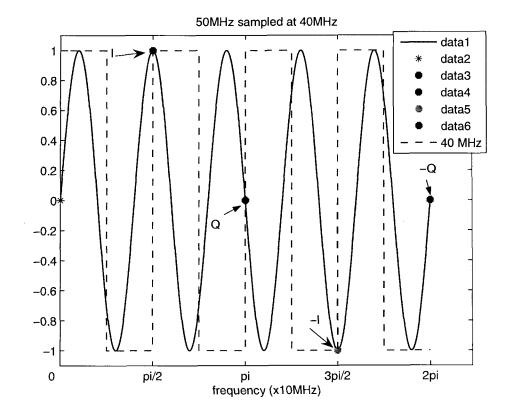

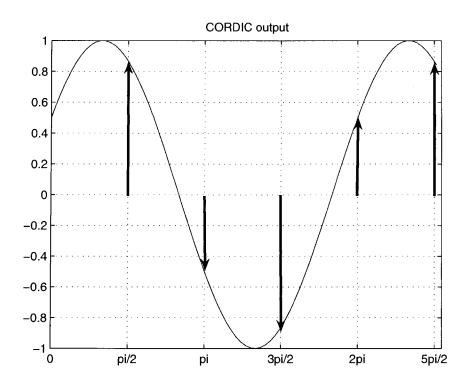

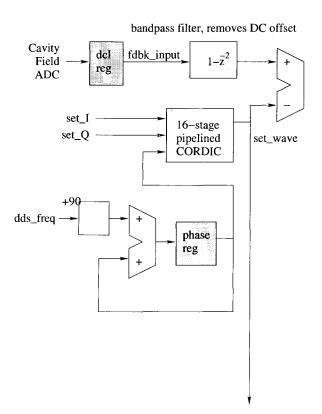

#### 4.5.2 Digital

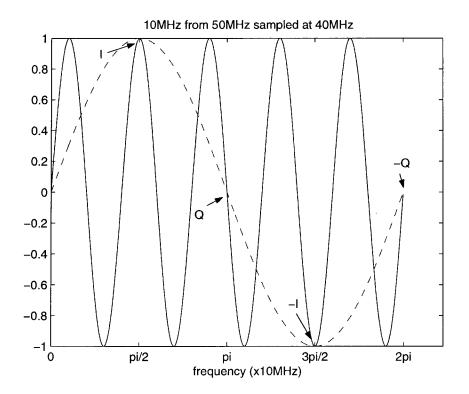

An alternate method of acquiring I/Q data is by sampling a signal at four points for each period. Hence, samples are taken at 90° intervals, assuming that the frequency is fixed. Assuming the first sample is at 0°, corresponding to I, the next sample is at 90°, or Q, the next sample is at 180°, or -I, and finally a sample at 270° corresponding to -Q. The ADC streams a series of I, Q, -I and -Q which can be manipulated once it is digitized.